#### FPGA SmartNIC N6010/6011 Intel based

Flexible Multi-port Ethernet Intel® AgileX Based SmartNIC

#### **Product Description**

The Silicom FPGA SmartNIC N6010/N6011 is a high-performance OEM hardware platform intended for hardware acceleration for mobile 4G and 5G Baseband Units or Distributed Units with two QSFP28 modules. The cards are based on the Intel N6000 and N6001. Example: supports up to 4 100MHz carriers Radio Units via 4x 25G eCPRI/CPRI with SFP28 modules, as well as interfacing to a Grand master via QSFP28 at 10/25G.

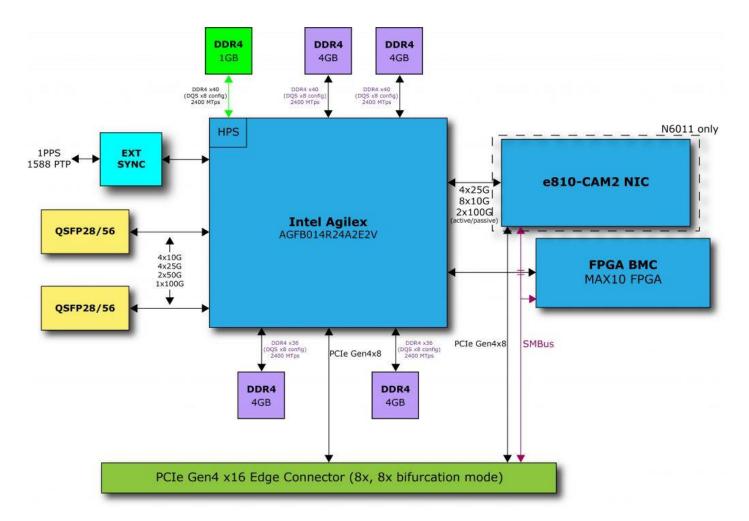

The card is based on an Intel® AgileX AGF014, which embeds a Hard Processor System (HPS) with four 64-bit Application Processing Units (ARM Cortex-A53) along with a powerful Programmable Logic part.

The design is set to work in ORAN LLS-C1 and C2 with the intention to be utilized with a 4G/5G IP stack interfacing at 3GPP functional split options 6 for CPRI or 7.2x for eCPRI.

The Silicom FPGA SmartNIC N6011 is supported by the Intel® Open FPGA Stack (OFS). The Intel OFS FPGA Interface Manager (FIM) provides a common developer interface to both application and acceleration function developers and includes drivers, Application Programming Interfaces (APIs) and an FPGA factory image.

Silicom validates each FPGA SmartNIC N6011 to support large scale deployments requiring FPGA acceleration. This OEM accelerator card is targeted for Intel® Xeon-SP and Intel® Xeon-D systems.

The Silicom FPGA SmartNic platform is targeted for market-specific acceleration in applications listed below:

#### Silicom FPGA N6010/6011 Use Cases:

- 4G/5G vRAN Acceleration

- Network Function Virtualization (NFV)

- Multi-Access Edge Computing (MEC)

- Video Transcoding

- Cyber Security

- High-Performance Computing

- Finance

# **Key Features**

- Intel® Agilex® FPGA

- Intel® e810-CAM2 NIC

- 2 x 100 GbE/4 x 25GbE/8 x 10GbE

- PCIe v4 x 8 (x16 physical)

# **Technical Specifications**

| Network Interface: |                                                                                                                                |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------|

| IEEE standard      | • IEEE 802.3 10GE, 25GE, 100GE                                                                                                 |

| Interfaces         | Physical interface: 2 x QSFP28/56 slots                                                                                        |

|                    | <ul> <li>Supports QSFP28/56 modules with Multimode SR (850nm), single<br/>mode LR (1310nm), multimode LRM (1310 nm)</li> </ul> |

|                    | <ul> <li>Data rate: Each module 100G, 4x25G, 4x10G</li> </ul>                                                                  |

|                    | Support for SyncE                                                                                                              |

| Interfaces:        |                                                                                                                                |

| Network                           | • 2x100GbE, using QSFP28/56                                                                                                                                                                                                                                                                                                                                                |  |  |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Host                              | <ul> <li>PCIe 4.0 x 16 (N6011 is bifurcated x8, x8)</li> <li>NCSI RBT</li> <li>Support for SMBUS</li> </ul>                                                                                                                                                                                                                                                                |  |  |

| General Technical Specifications: |                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| NIC details                       | Intel® E810-CAM2  Interfaces to PCIe 4.0 x8  Supports 2x100GE (active/protect), 4x25GE and 8x10GE                                                                                                                                                                                                                                                                          |  |  |

| FPGA Details                      | Intel® Agilex™ AGF014  • 1.4M Logic Element Fabric  • Provides Ethernet or Ethernet and Common Public Radio Interface (CPRI) interface over QSFP28/56 ports  • P-Tile – Provides PCIe Gen4 x8 interface to the host  • Hard Processor System (HPS)  • DDR4 Memory controllers interfacing to the FPGA fabric  • Platform Management Communications Interface (PMCI) module |  |  |

| Configuration                     | <ul> <li>Configuration flash can be made to support multiple boot images for automatic fallback to factory default image</li> <li>Upload of FPGA configuration to flash via PCIe</li> <li>Direct FPGA configuration via the onboard JTAG dongle</li> </ul>                                                                                                                 |  |  |

| On-board Memory                   | <ul> <li>8 GB DDR4 memory, with ECC (2 channels)</li> <li>8 GB DDR4 memory, without ECC (2 channels)</li> <li>1 GB DDR4 memory for HPS</li> <li>280 MB Flash memory for non-volatile storage</li> </ul>                                                                                                                                                                    |  |  |

| On-board Clock                    | <ul> <li>PCle clock: 100 MHz</li> <li>8 output reprogrammable clock generator</li> <li>Supports network synchronization</li> </ul>                                                                                                                                                                                                                                         |  |  |

| Additional Board Support          | <ul> <li>On-board power and temperature sensors (via SMBus/I2C)</li> <li>FPGA controlled Link and Activity LED for each port. 2 for each QSFP28</li> <li>Board status LEDs</li> <li>FPGA Reset via host I2C</li> </ul>                                                                                                                                                     |  |  |

| Environment                       | <ul> <li>Full height, ½ length 111.28 x 167.65 mm with bracket</li> <li>Storage temperature: -40 - 65°C -40 - 149°F</li> <li>Operating temperature (card inlet): -5 - 50°C, 23 - 122°F</li> <li>Operating humidity: 5 - 85%</li> <li>Hardware compliance: RoHS, FCC, CE</li> </ul>                                                                                         |  |  |

| Power                  | <ul> <li>Max 125W, above 75W PCIe AUX power must be used</li> <li>Passive cooling</li> <li>Power and temperature monitoring via SMBus/I2C</li> <li>PCIe AUX power connector available</li> </ul>                                                       |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Manageability Features | <ul> <li>Full card BMC solution host communication via SMBus (PLDM &amp; NC-SI)</li> <li>FPGA image remote update capability</li> <li>Full security implementation using MAX10 FPGA as RoT</li> </ul>                                                  |

| Networking             | <ul> <li>A configurable packet processor IP core</li> <li>Extensive configuration API</li> <li>Packet forwarding and bridging across network, main host and SoC</li> <li>Parsing, match and action operations</li> <li>Bandwidth rate limit</li> </ul> |

| Hardware Acceleration  | <ul><li>SR-IOV, 256 virtual functions</li><li>32 physical functions</li></ul>                                                                                                                                                                          |

| Software Support       | <ul> <li>Open FPGA Stack (IOFS)</li> <li>Contrail</li> <li>OVS</li> <li>SRv6</li> <li>vFW acceleration</li> <li>4G and 5G vRAN enablement package</li> <li>DPDK</li> <li>BBDev</li> <li>FlexRAN</li> </ul>                                             |

# **Order Information**

| P/N               | Notes:                                         |

|-------------------|------------------------------------------------|

| FB2CG2@AGF14-A1S2 | Silicom FPGA SmartNIC N6011 (base + Intel NIC) |

| FB2CG1@AGF14-A0S2 | Silicom FPGA SmartNIC N6010 (base)             |

1v1