### FPGA SmartNIC FB2CDG1@AGM39D-2 Intel® based

Flexible Multi-port Ethernet Intel® Agilex M Based SmartNIC

### **Product Description**

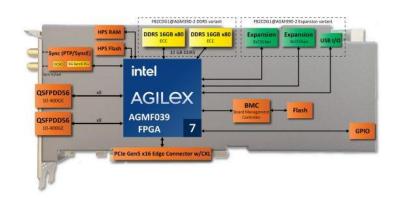

The Silicom FPGA SmartNIC FB2CDG1@AGM39D-2 is a high-performance programmable PCIe Server adapter based on the Intel® Agilex™ M-series AGMF039 FPGA (option for AGMF032). The Agilex-M™ is an extremely powerful FPGA which also features up to on-chip 32GB HBM2e memory providing an unprecedented 2 x 2.6 Tbps HBMe2 bandwidth. The card is equipped with 2 x QSFPDD56 for supporting 2x 400GE, as well as a wide range of other link speed combinations like 16x10/25GE or even 8x100G with the appropriate breakout modules and link partners.

The FB2CDG1@AGM39D-2 is made in 2 primary variants: One variant with 2 banks of DDR5 for 32GB DDR5 on the PCB. The second variant with 2 x ARF6 connectors with 16x32Gbps. The ARF6 connectors add unprecedented flexibility in host bandwidth and network connectivity. Via an adaptor cable, an additional PCIe Gen4 x16 connector can be employed for additional host bandwidth. The same connectors can alternatively be used with Fireflytm cables for connecting an additional 2x 8xSFP28 or 2x 2xQSFP28 for higher Ethernet link capacity to the solution in appliances. The connectors can also be used for direct connection of two boards or to connect multiple cards in series.

The AGM FPGA series features CXL 1.1 and 2.0, providing heterogeneous processing and computing in performance-intensive workloads like AI, machine learning and analytics.

#### **Target Applications**

- Network Security & Telemetry

- Virtual Firewall (vFW)

- DDoS Mitigation

- o IP Security (IPsec)

- Transport Layer Security (TLS)

- Packet monitoring and analytics

## Network Functions

- 5G/6G User Plane Function (UPF)

- o 5G Access Gateway Function (AGF)

- Virtual Broadband Network Gateway (vBNG)

- Virtual Application Delivery Controller

- o Traffic Management

- Carrier Grade Network Address Translation (CGNAT)

- Cloud Gateway

- Application Access Gateway

- General interconnect

- o ISP Interconnections

#### **Application acceleration**

- o Data analysis offload

- Sensor aggregation and analysisSensor recording

# **Key Features**

#### Silicom FPGA SmartNIC FB2CDG1@AGM39D-2

- Intel® Agilex™ AGMF039 FPGA

- o 2 x QSFPDD56 ports

- o HBM2e: 32GB

- o 2 x ARF6 expansion connectors each with 8x28Gbps

- o PCIe x16 Gen5 w/CXL

- o 5G SyncE PLL with Silicom TimeSync Solution (STS)

- o Dedicated RAM for HPS

- o GPIO

- Intel® Max® 10 Board Management Controller 0

- Dual slot passive heat sink (single slot optionable)

- o On-board power and temperature sensors

- FPGA controlled link and status LEDs

## **Technical Specifications**

| Network Interface:                |                                                                                                                                                                                                                                             |  |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IEEE standard                     | • IEEE 802.3 400GbE, 200GbE, 100GbE, 25GbE, 10GbE                                                                                                                                                                                           |  |

| Interfaces                        | <ul> <li>Physical interface: 2 x QSFPDD56 slots</li> <li>Multimode SR4/SR8 (850nm), Single Mode LR4/LR8 (1310nm) or Direct<br/>Attached Copper (Twinax)</li> <li>Data rate: 2x400, 4x200, 2x200, 1x400, 4x100, 16x25, 16x10 Gbps</li> </ul> |  |

| Host Interface:                   |                                                                                                                                                                                                                                             |  |

| PCI bus                           | • PCle 5.0 x16                                                                                                                                                                                                                              |  |

| General Technical Specifications: |                                                                                                                                                                                                                                             |  |

| FPGA Details                      | Intel® Agilex™ AGMF039                                                                                                                                                                                                                      |  |

|                                   | R47A package, with 3 x F and 1 x R tile                                                                                                                                                                                                     |  |

|                                   | Speed grade -2                                                                                                                                                                                                                              |  |

|                                   | ARM HPS                                                                                                                                                                                                                                     |  |

|                          | <ul><li>32GB HBM2e</li><li>3 x 600GE HIPs (F-tiles)</li></ul>                                                                                                                                                               |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configuration            | <ul> <li>Configuration flash can be made to support multiple boot images for automatic fallback to factory default image</li> <li>Upload of FPGA configuration to flash via PCIe – with supported image and tool</li> </ul> |

| On-chip Memory           | HBM2e, 32GB in Agilex™ M-series FPGA                                                                                                                                                                                        |

| On-board Memory          | DDR4, 4GB+ECC for HPS                                                                                                                                                                                                       |

| Expansion Connectors     | <ul> <li>2 x 32pin ARF6 for 2x 8x25Gbps</li> <li>Allows an extra x16 PCIe Gen4 via adapter for extra Host PCI BW and resources</li> <li>Allows connection for additional network ports</li> </ul>                           |

| On-board Clock           | <ul> <li>PCle clock: 100 MHz</li> <li>DPLL ZL30793</li> <li>Jitter cleaner</li> <li>8 output reprogrammable clock generator (PLL) with SyncE support</li> </ul>                                                             |

| Additional Board Support | <ul> <li>On-board power and temperature sensors (via SMBus/I2C)</li> <li>LEDs for board status and board management</li> </ul>                                                                                              |

| Physical Dimensions      | <ul> <li>Weight: ~1600 g (TBD)</li> <li>Full height, 123.4 mm</li> <li>¾ length, 254.0 mm (+bracket)</li> <li>Dual Slot Passive</li> </ul>                                                                                  |

| Environment              | <ul> <li>Storage temperature: TBD</li> <li>Operating temperature: TBD</li> <li>Hardware compliance: RoHS, FCC Class A, CE, UL</li> </ul>                                                                                    |

| Thermal Design           | Passive heat sink targeted to dual slot                                                                                                                                                                                     |

| Max Power                | <ul> <li>Max: 410W *)</li> <li>65 W max from the PCie slot</li> <li>345 W max from the 12V high power Aux connector *) (including optical modules)</li> </ul>                                                               |

|                      | *) The combined server-PCle card solution may be limited in average power consumption by thermal constraints                                                                                                                            |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Port LEDs            | <ul> <li>2 x Link/ ACT for the 2 x QSFPDD56, on bracket</li> <li>1 x multi color status LED, on bracket</li> </ul>                                                                                                                      |

| Time Synchronization | <ul> <li>Silicom TimeSync Solution (STS)</li> <li>IEEE 1588-2019, G8273.2, G8273.4 (T-BC/T-TSC), G8262(SyncE)</li> <li>1PPS In/Out, 10Mhz In/Out (optional)</li> <li>OCXO</li> <li>PTP stack: LinuxPTP (ptp4l) on HPS or x86</li> </ul> |

| Board Management     | <ul> <li>Intel® Max® 10 FPGA Board Management Controller</li> <li>Voltage level monitoring</li> <li>Thermal shut-down protection</li> <li>Over current protection on 12V input</li> </ul>                                               |