#### Silicom C5010X Data Center FPGA IPU NIC

Dual port SFP28 25G Ethernet PCIe FPGA IPU NIC Intel® based

#### **Product Description**

Silicom C5010X Data Center FPGA IPU NIC Intel® based is an advanced data processing network interface controller, featuring cutting edge I/O and data processing capabilities, optimized for virtualized cloud, cloud native or bare metal virtualization.

Silicom C5010X can be offered with complete implementation of I/O workload using industry standard interfaces, allowing

Silicom C5010X to be operated using stock virtio and NVMe drivers, implementing a true hardware virtio and NVMe PCIe interface.

Combining two powerful engines – Intel® Stratix® 10 DX 1100 FPGA and Intel® Xeon® D-1612 SoC (x86 CPU, 4 cores, 8 threads) – Silicom C5010X data processing NIC brings together the power and flexibility of FPGA and the wealth of the x86 ecosystem.

A unique 3-way path for application optimization guarantees fast results. The presence of a x86 based CPU allows you to leverage existing software assets, where the FPGA flexibly extremely enables performant data path implementation:

- 1) In the first stage, the card can serve as a standard NIC with minimal configuration changes, with minimal orchestration modification;

- 2) Second stage include a migration of data plane and VM switching functionality from main host down to x86 CPU cores on card;

- 3) The third stage involves data path implementation on the FPGA.

Using the offered IP, the Silicom C5010X can be developed and deployed as a virtio network accelerator, a virtio storage accelerator, a NVMe storage (network) controller, a RDMA OFED controller, either separately or all at the same time. Further

implementations such as flow filtering, encryption, compression, deduplication, and machine learning, are facilitated by C5010X facilitates as complete infrastructure implementation on an NIC.

As the data path is implemented on the card, fewer risks and vulnerabilities are left to the cloud data center infrastructure.

Storage data paths in a cloud environment are often associated with the use of a storage attached network (SAN), serving the compute nodes over the network. The use of an x86 CPU core NIC with FPGA facilitates for allows relatively easy implementation of storage volume virtualizations, accessible on the host using stock storage software stacks, such as NVMe.

#### **Key Use Cases**

- Virtual Cloud

- Bare Metal Cloud

- NVF

- Secure Infrastructure

- Cloud Storage

# **Key Features**

- Intel® Xeon® D-1612 @ 1.5GHz 4 core, 8 threads

- Intel® Stratix® 10 DX 1100

- virtio-net and virtio-blk over PCle

- Dual 25GbE

- PCIe v4 x 8 (x16 physical)

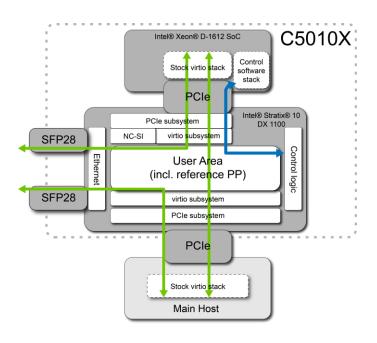

Figure 1 – Various data paths (green) and control paths (blue) are enabled on Silicom C5010X

# **Technical Specifications**

| Network Interface |                                                                                                                                                                                                                                                                                         |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IEEE standard     | IEEE 802.3 10GE, 25GE                                                                                                                                                                                                                                                                   |  |

| Interfaces        | <ul> <li>Physical interface: 2 x SFP28 slots</li> <li>Supports SFP+/SFP28 modules with Multimode SR (850nm), single mode LR (1310nm), multimode LRM (1310 nm), or Direct Attached Copper (Twinax) and others</li> <li>Data rate: 2x10, 2x25, Gbps</li> <li>Support for SyncE</li> </ul> |  |

| Interfaces        |                                                                                                                                                                                                                                                                                         |  |

| Network           | ■ Dual 25GbE, using SFP28                                                                                                                                                                                                                                                               |  |

| Host              | <ul> <li>PCle gen4 x 8 (x16 physical)</li> <li>NCSI RBT</li> <li>Support for SMBUS</li> </ul>                                                                                                                                                                                           |  |

| SoC               | <ul><li>PCle v3 x 8</li><li>USB NIC</li><li>UART</li></ul>                                                                                                                                                                                                                              |  |

| General Technical Specifications |                                                                                                                                                                                                                                                                                 |  |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SoC details                      | Intel® Xeon® D-1612  4 x86 64 bit cores @1.5GHz  8 threads  6MB cache  VT-d, VT-x  Intel® AVX2  AES-NI  16GB DDR ECC                                                                                                                                                            |  |

| FPGA Details                     | Intel® Stratix 10 DX 1100  Intel® Hyperflex™ core architecture  Intel® Embedded Multi-die Interconnect Bridge (EMIB)  PCIx Gen4 x16 hard IP, SRIOV  Fixed point and IEEE 754 compliant floating-point variable precision digital signal processing (DSP) block  Internal memory |  |

|                            | <ul> <li>M20K, 107Mb</li> <li>eSRAM, 47.25Mb</li> <li>MLAB</li> <li>1,325,000 ALM</li> <li>Quad-core 64-bit Arm® Cortex®-A53 embedded processor @1.5 GHz</li> <li>4GB DDR</li> </ul>                                                                                               |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configuration              | <ul> <li>Configuration flash can be made to support multiple boot images for automatic fallback to fail safe</li> <li>Upload of FPGA configuration to flash via PCIe</li> <li>Direct FPGA configuration via the onboard JTAG dongle</li> </ul>                                     |

| On-board Memory            | <ul> <li>16GB DDR ECC for SoC</li> <li>4GB DDR for FPGA</li> <li>User configurable space in flash RAM for permanent storage</li> <li>Configuration flash RAM for boot images</li> </ul>                                                                                            |

| On-board Clock             | <ul> <li>PCle clock: 100 MHz</li> <li>Core Clock 125Mhz</li> <li>2 x differential 312.5 MHz SerDes clock for Ethernet</li> <li>2 x differential 266.67 MHz/300MHz/333.33MHz clock for Memory</li> <li>Calibration clock 125MHz, 100MHz, 25MHz</li> <li>50 MHz clock</li> </ul>     |

| Additional Board Support   | <ul> <li>On-board power and temperature sensors (via SMBus/I2C)</li> <li>FPGA controlled Link and Activity LED for each port. 2 for each SFP28</li> <li>Board status LEDs</li> <li>FPGA Reset via host I2C</li> </ul>                                                              |

| Environment                | <ul> <li>Full height, ½ length 111.15 x 167.65 mm with bracket</li> <li>Storage temperature: -30 - 70°C -22 - 158°F</li> <li>Operating temperature (card inlet): 0 - 55°C, 30 - 130°F</li> <li>Operating humidity: 20 - 80%</li> <li>Hardware compliance: RoHS, FCC, CE</li> </ul> |

| Power                      | <ul> <li>Max 75W</li> <li>Passive cooling</li> <li>Power and temperature monitoring via SMBus/I2C</li> </ul>                                                                                                                                                                       |

| Management                 | <ul> <li>SoC boot options: PXE, SATA</li> <li>SoC control interfaces: USB, UART, network</li> </ul>                                                                                                                                                                                |

| Networking                 | <ul> <li>A configurable packet processor IP core</li> <li>Extensive configuration API</li> <li>Packet forwarding and bridging across network, main host and SoC</li> <li>Parsing, match and action operations</li> <li>Bandwidth rate limit</li> </ul>                             |

| 3rd party solution support | ■ Napatech Link™ Virtualization Software and SmartNIC solution Extensive configuration<br>API                                                                                                                                                                                      |

# **Order Information**

| Ordering Information |  |

|----------------------|--|

| FB2XXVG@S10D11-HDNP  |  |

v1.1